Vertical Stacking: A Tall Claim?

Another concern with vertically stacked silicon architecture is maintaining signal integrity and managing crosstalk. As transistors and other components are positioned closer together in the vertical axis, the potential for electromagnetic interference between high-speed signals escalates. This interference, known as crosstalk, can significantly impact the performance of the chip by causing signal degradation.

Addressing these concerns requires a sophisticated understanding of electromagnetic coupling and the implementation of advanced design strategies. Crosstalk in vertically stacked silicon occurs primarily due to capacitive and inductive coupling between signal lines. Capacitive coupling is when the signal from one line interferes with another through a capacitor-like effect, while inductive coupling occurs through an inductor-like interaction between lines. Both phenomena can lead to signal distortion and loss of integrity, posing significant challenges in high-density chip designs.

Several strategies have been developed to mitigate crosstalk and preserve signal integrity. One such approach involves the use of dummy metal fill, which helps to isolate signal lines from each other, reducing the likelihood of interference. Moreover, 3D full-wave modeling and simulation of Through-Silicon Vias (TSVs) have been used to characterize and predict crosstalk under various configurations and conditions. This modeling enables the optimization of TSV design and placement, reducing the impact of crosstalk in high-frequency applications.

In addition to physical design alterations, electrical characterization techniques, such as evaluating S-parameters (reflection and transmission coefficients), are utilized to assess and optimize the signal integrity of the interconnections. With the help of simulated data streams through the TSVs and analyzing eye diagrams, engineers understand the impact of design choices on signal integrity and make informed adjustments.

To ensure the maximum system performance, it’s crucial to consider the role and location of signal and ground Vias in the 3D design. Adjusting these parameters can significantly reduce the magnitude of crosstalk, particularly in high-frequency applications where crosstalk can be most detrimental. Other Solutions To Reduce Crosstalk:

- Advanced Shielding Techniques: Employing shielding methods at the chip level to isolate signal paths physically and reduce the impact of electromagnetic interference.

- Improved Circuit Design: Optimizing circuit layouts to minimize the proximity of high-speed signal lines and employing differential signaling where possible to reduce susceptibility to crosstalk.

- Material Innovations: Exploring advanced materials with better electromagnetic properties for use in chip fabrication, which could inherently reduce crosstalk and improve signal integrity.

- Signal Conditioning: Using signal conditioning techniques such as buffering and the use of repeaters to strengthen signal integrity over longer distances within the chip.

- Alternative Interconnect Technologies: Exploring other interconnect technologies beyond TSVs, such as optical interconnects or wireless chip-to-chip communication, which might offer different trade-offs in terms of signal integrity and crosstalk.

- Dynamic Signal Management: Implementing intelligent systems within the chip that can dynamically adjust signal strength and routing based on real-time analysis of signal integrity and crosstalk levels.

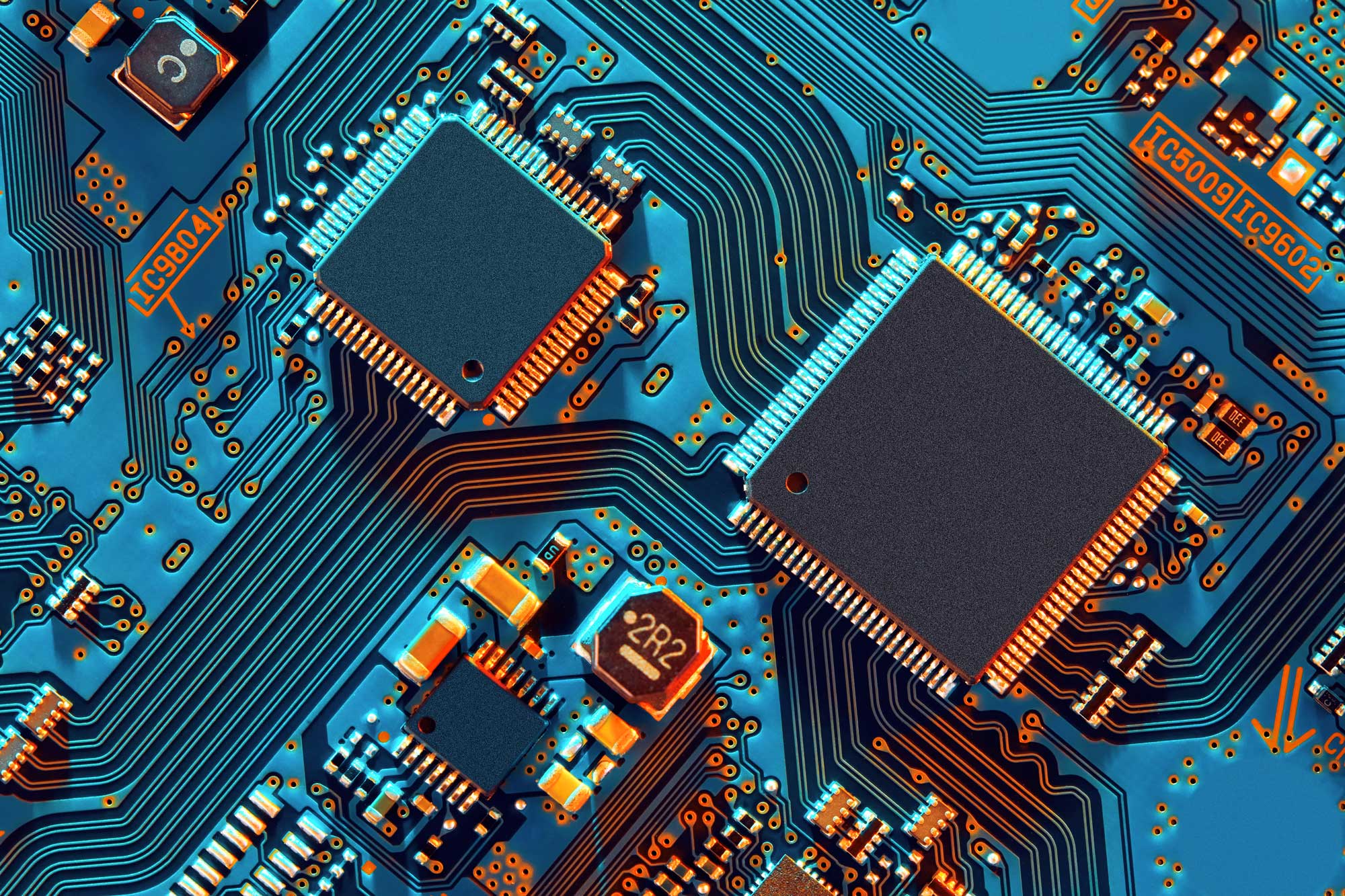

Vertical stacking in semiconductors is like building skyscrapers instead of single-story houses. This method stacks transistors and other parts on top of each other (the Z-axis), making chips more compact and efficient. It helps pack more components into a small space and makes connections between them shorter and faster.

This spatial optimization translates to shorter and more efficient pathways for electronic signals, drastically reducing the latency and power consumption typically associated with longer interconnects. This is key for tiny, sub-3nm chips, as it boosts computing power, saves energy, and adds more functions to small chips, crucial for things like advanced computing and wearables.3 The result is a notable augmentation in the chip’s computational prowess and energy efficiency—a critical factor in applications demanding high processing power within minimal form factors.

This is not a revolutionarily new idea though. As early as 2015, Stanford engineers unveiled the Skyscraper-style chip design that boosts performance by a factor of a thousand.4 Imagine a smartwatch that’s 5x thinner yet offers 100x faster computing power, thanks to vertically stacked silicon chips. This technology enables devices like ultra-slim laptops to perform complex tasks like real-time 4K video editing or running advanced AI algorithms, tasks that once required a high-end desktop. This leap in efficiency and power in such compact devices revolutionizes how we interact with technology in our daily lives.

However, this vertical stacking approach has its own challenges. Packing components so closely can cause overheating, make power delivery complex, and complicate chip-making and testing. Plus, at these tiny scales, quantum effects come into play, requiring new materials and design methods to manage these issues effectively. We will explore the various problems of vertical stacking architectures and their potential solutions.